日立製作所は6月15日、実社会の複雑な問題の高速処理を実現し、問題規模に応じてスケーラブルに構成可能な世界最大規模のCMOSアニーリングマシンを開発したと発表した。

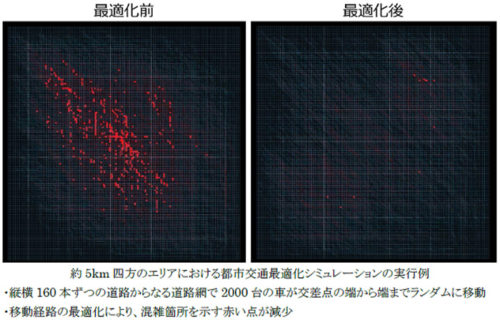

都市での交通渋滞の解消やグローバルサプライチェーンでの物流コスト低減などをはじめとする、実社会の複雑な問題を高速に解くために、問題規模に応じてスケーラブルに構成可能なCMOS アニーリングマシンを開発したもの。

開発したCMOSアニーリングマシンは、CMOSアニーリングチップ(FPGA)を25枚接続することにより世界最大規模の10万2400パラメータの問題に対応でき、従来、拡張が制限されていたアニーリングマシンの性能を、複数チップの接続技術で拡張できることを実証した。

今年8月より、このマシンを、最適化問題を課題としているパートナー向けにクラウドサービスとして公開し、CMOSアニーリングマシンを活用したソリューション協創に取り組んでいくとしている。

CMOSアニーリングマシンとは、磁性体の性質を説明するために考案されたイジングモデルを用いて組合せ最適化問題を解くために日立が開発している新型コンピュータのこと。